4.1 Overview

The objective of Stage II is to enable a minimal boot path memory initialization code execution that successfully installs permanent memory.

4.1.1 Major Execution Activities

- Complete execution of the memory initialization module.

- Discover, train and install permanent memory.

- Migrate the temporary memory/stack to permanent memory.

- Migrate any code modules from temporary RAM to permanent memory.

- Perform cache configuration for a post-memory environment.

- Execute memory installed notification actions.

Stage II Functionality |

|---|

| Non-volatile storage read-only access |

| Pre-memory silicon policy initialization |

| Basic services like cache and CPU IO |

| Initialization of decompression capability |

| Memory initialization and basic memory test |

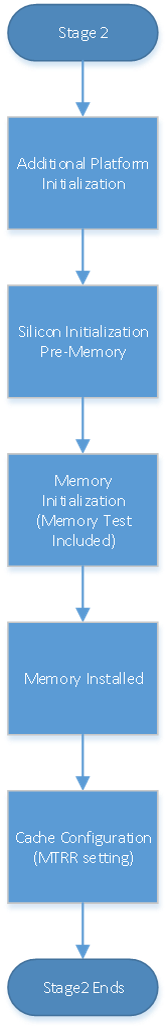

4.1.2 Main Control Flow

Stage II extends the Stage I control flow by executing the platform and silicon initialization required for memory initialization. The stage is completed when permanent memory is installed. Since execution prior to memory initialization typically occurs in a resource-constrained environment, the code in this stage is not compressed. To simplify silicon enabling which may be opaque to the board engineer in the form of a binary blob, Stage II enabling does not strictly constrain the extent of silicon initialization. In particular, it is recommended to perform standard security lock functionality such as register locks, privilege level changes, and other actions that are in the system requirements to reduce conditional logic and therefore potential for error in enabling those settings. This only pertains to security settings within the chipset. This does not include larger industry standard security features such as UEFI Secure Boot and TCG measured boot. Those features are enabled in Stage V Security Enable.